To ensure high-quality integration delivery and increase confidence in tape-out, a range of techniques are employed to achieve full verification closure. As chip design complexity increases, coverage metrics have become essential for guiding and optimizing the verification process. Integrated tools and rigorous methodologies are adopted to improve coverage, requiring deep domain expertise and advanced techniques. At Faraday, we have successfully established a robust infrastructure and business model that supports a wide range of applications.

SystemVerilog Assertion (SVA)

SystemVerilog assertions validate design behavior and provide functional coverage, ensuring high-quality integration in SoC design. This technology is widely applied across domains such as clock, reset, protocol, and power, enabling early detection of design flaws.

Universal Verification Methodology (UVM)

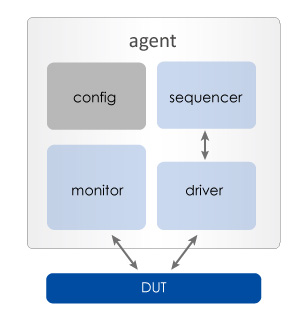

UVM is a methodology and library that encapsulates best practices for efficient, comprehensive verification. It provides a framework for coverage-driven verification (CDV) that:

- Reduce effort and time across hundreds of tests

- Establish clear, measurable goals for thorough verification

Additionally, IP-XACT automates the generation of UVM register packages, enabling more efficient HW/SW interface verification. This streamlines the verification process at the register level.

Faraday establishes a verification environment based on UVM test bench architecture, integrating various VIP models to validate system-level functionality, particularly for complex SoCs, providing a solid and reliable verification framework.

Low Power

The need to reduce power consumption has driven the adoption of various methods, such as power domain partition and clock gating. To achieve optimal low power performance and avoid late-stage redesigns, RTL-level verification is essential, including:

- Comprehensive functional verification both before and after power optimization is applied

- Ensuring hardware functionality aligns with software control sequences

Clock Domain Crossing

Modern designs often integrate multiple clocks, and synchronization issues can result in system failures. Identifying and resolving potential problems in multi-clock designs is a critical part of Faraday's verification flow.

Verification IP

SystemVerilog and UVM offer a standardized framework for exchanging verification IP (VIP) and testbenches across teams. At Faraday, UVM VIPs are extensively used throughout IP-level and system-level verification processes. Additionally, we maintain a diverse repository of VIP categories to support a wide range of SoC verification requirements.