Faraday 16Gbps multi-protocol programmable SerDes PHY IP in UMC 28HPC+ process is designed with a system-level approach to provide optimization of power, performance and area to meet the growing needs for high bandwidth and low latency in the applications of consumer, access layer networking device to core/enterprise layer.

The silicon verified 16Gbps SerDes PHY supports the optimization of SoC chip designs to enable the infrastructure of 10G/40G Ethernet, PCIe 4.0, 5G, and most xPON applications. Compared with the other latest Serdes solutions, it is the only solution that supports both PCIe 4.0 and 10G xPON ONU/OLT in 28nm node.

This full-duplex, high-performance and many-protocols compatible SerDes solution comes with a scalable PMA which can be applied to a wide range of applications across copper and backplane channels with total insertion loss more than 30dB. It is also compatible with standard PCS and controller, and provides flexible design environment for users to customize PCS and controller integration.

Highlights

- Support PCIe G1 to G4 with PCS soft-macro supporting PIPE 4.4.1

- Support xPON applications: Sym/Asym GPON, Sym/Asym 10GPON, Sym EPON, Sym/Asym 10GEPON

- Support IEEE 802.3 1G to 40G backplane (KX, KX4/XAUI, KR & KR4), port side (XFI, SFF-8431/SFI and CR4)

- Support JESD204B/C for high-speed ADC/DAC and FPGA interface

- Support SGMII and QSGMII (1.25 to 5G)

- Support CEI-6G and CEI-11G

- Support Serial Rapid IO (SRIO)

- Support CPRI

- Multi-Interface to enable 3rd party’s PCS/MAC’s direct connection to PMA

- Soft PCS IP available for PCIe 4.0 and bifurcation applications

- PMA data width for 16/20/32/40 bits

- Full-duplex lane configuration of x1, x2, x4

- Ultra-low-power 3 TAP FIR voltage-mode driver with programmable swing and amplitude

- Receiver with adaptive CTLE/VGA equalizer, and 5 TAP DFE

- Multiple internal/external loopbacks (TX to RX, RX to TX, RX loopback after S2P with RX clock)

- On-chip eye scan monitor for testing

- Built-in power-saving states

- Built-in PRBS & programmable pattern generator and checker

- FOM for link training

- Extensive auto-calibration and BIST engine for performance tuning and self-diagnostics

- Support up to 600 ppm offset and up to 5000ppm SSC

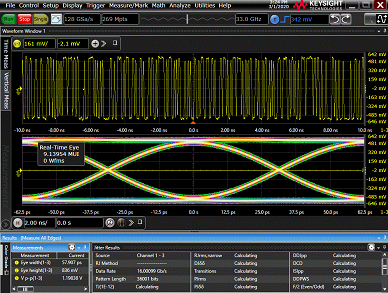

16Gbps TX EYE@PRBS31